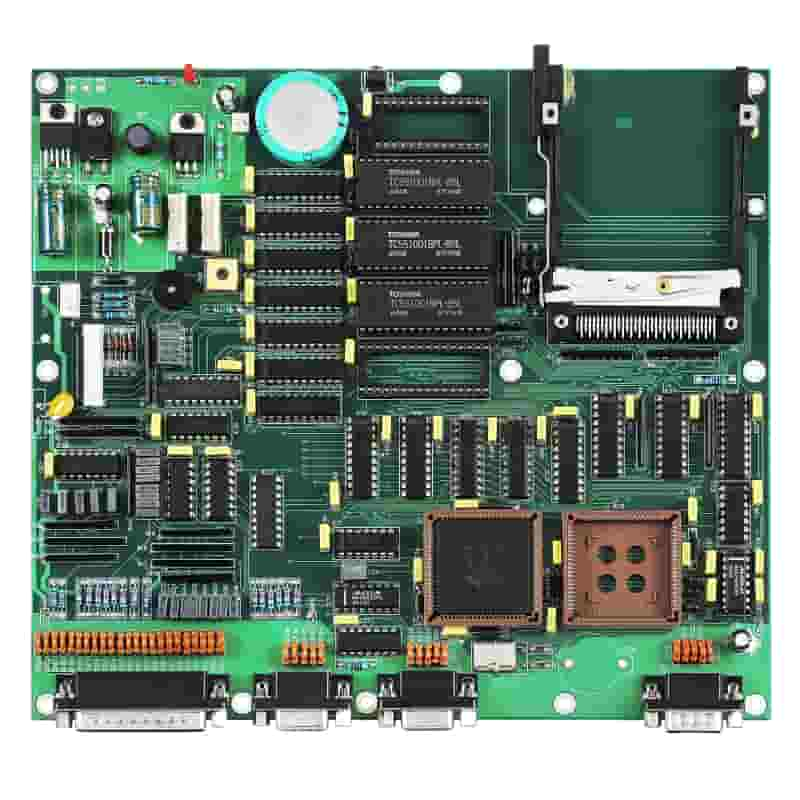

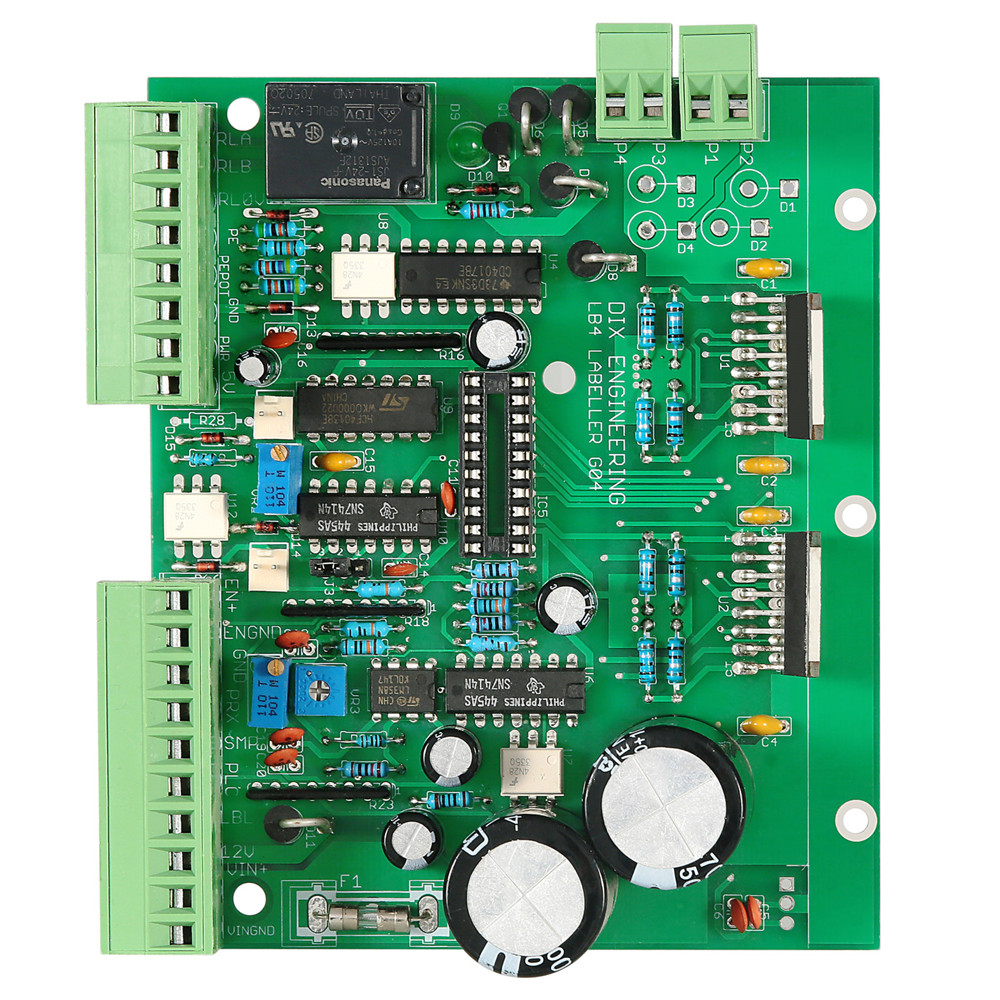

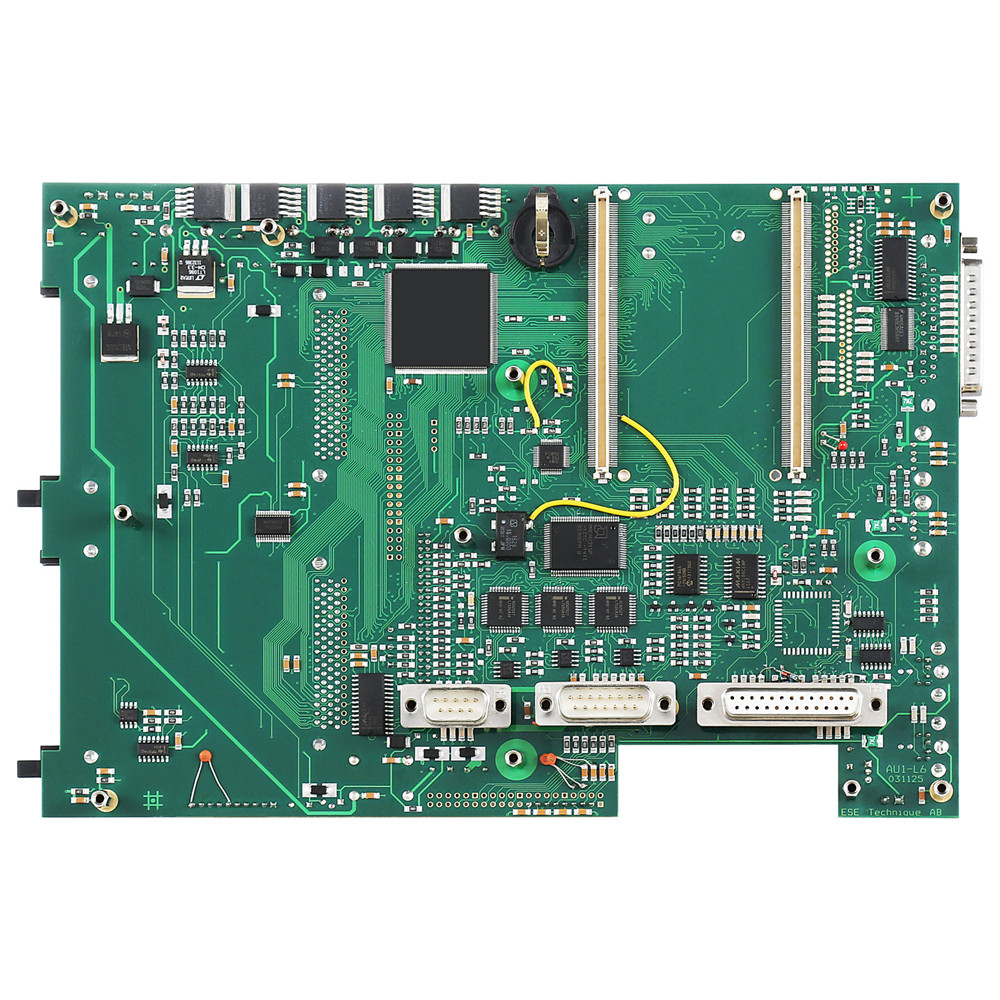

Computer an Peripherieger PCBA Verwaltungsrot

Produit Fonktioun

● -Material: Fr-4

● -Layer Count: 14 Schichten

● -PCB Dicke: 1,6 mm

● -Min. Trace / Space Outer: 4/4mil

● -Min. Gebuert Lach: 0,25 mm

● -Via Prozess: Zelt Vias

● -Surface Finish: ENIG

PCB Struktur Charakteristiken

1. Solderresistant Tënt (Solderresistant / SolderMask): Net all Kupferflächen mussen Zinndeeler iessen, sou datt d'Net-Zinn-giess Gebitt mat enger Schicht vum Material (normalerweis Epoxyharz) gedréckt gëtt, déi d'Kupferoberfläche isoléiert vum Zinn ze iessen vermeiden Net-Soldering. Et gëtt e Kuerzschluss tëscht den tinned Linnen. No verschiddene Prozesser ass et a gréng Ueleg, rout Ueleg a blo Ueleg opgedeelt.

2. Dielektresch Schicht (Dielektresch): Et gëtt benotzt fir d'Isolatioun tëscht Linnen a Schichten z'erhalen, allgemeng bekannt als de Substrat.

3. Surface Behandlung (SurtaceFinish): Well d'Kupferfläche liicht am allgemengen Ëmfeld oxidéiert gëtt, kann et net tinnéiert ginn (schlecht Solderbarkeet), sou datt d'Kupferfläche, déi tinnéiert gëtt, geschützt gëtt. D'Schutzmethoden enthalen HASL, ENIG, Immersion Silver, Immersion TIn, an organesch Solderkonservéierungsmëttel (OSP). All Method huet seng eege Virdeeler an Nodeeler, kollektiv als Uewerfläch Behandlung bezeechent.

PCB Technesch Kapazitéit

| Schichten | Mass Produktioun: 2 ~ 58 Schichten / Pilot lafen: 64 Schichten |

| Max. Dicke | Mass Produktioun: 394mil (10mm) / Pilot lafen: 17.5mm |

| Material | FR-4 (Standard FR4, Mid-Tg FR4, Hi-Tg FR4, Bläi-fräi Montagematerial), Halogenfräi, Keramik gefüllt, Teflon, Polyimid, BT, PPO, PPE, Hybrid, Partiell Hybrid, etc. |

| Min. Breet / Abstand | Innere Schicht: 3mil/3mil (HOZ), Bausseschicht: 4mil/4mil (1OZ) |

| Max. Kupfer Dicke | UL zertifizéiert: 6.0 OZ / Pilot lafen: 12 OZ |

| Min. Lach Gréisst | Mechanesch Bohr: 8mil (0.2mm) Laserbohr: 3mil (0.075mm) |

| Max. Panel Gréisst | 1150 mm × 560 mm |

| Aspekt Verhältnis | 18:1 |

| Uewerfläch Finish | HASL, Immersion Gold, Immersion Tin, OSP, ENIG + OSP, Immersion Silver, ENEPIG, Gold Finger |

| Special Prozess | Buried Hole, Blind Hole, Embedded Resistance, Embedded Capacity, Hybrid, Partiell Hybrid, Partiell High Density, Back Drilling, and Resistance Control |